本文以2022R2 HFSS 3D Layout示范四种从封装经PCB到连接器的端对端仿真方法,比较其仿真差异并说明各自所长。

- 前言

BGA封装(Ansys SIwave解决方案)

PCB(Ansys SIwave)

连接器(HFSS解决方案)

如果要把高速传输通道的这三部分一起模拟,在HFSS 3DL内该如何做呢?

有四种方法,各有所长,故事继续看下去 ...

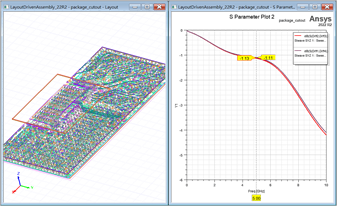

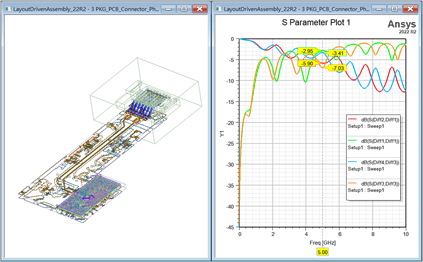

- 封装+PCB+连接器 以3DL Assembly连接求解

这是2016年(R17)开发的方法,其概念是把封装、PCB、连接器都先各自设定好自己的端口与指定求解方式(HFSS/SIwave),最后在HFSS 3D Layout内通过拖拽(或Copy/Paste)+[Place Design]+[Interface]\[Add Interface Ports on Unconnect

Pins]+[LNA analysis],得到整个串接的S参数。

其优点是可以PCB板子/BGA封装用SIwave解算,而连接器以HFSS解算,最后3DL Assembly就是把这些各别解出的S参数“串接”起来的结果,求解速度快很多,但限制是没有考虑这三部分彼此间的空间(上下)耦合。

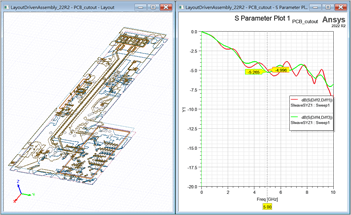

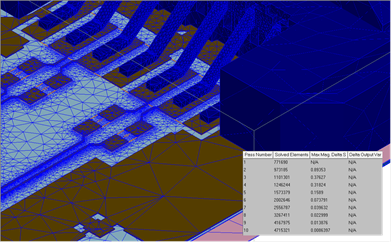

- 封装+PCB+连接器

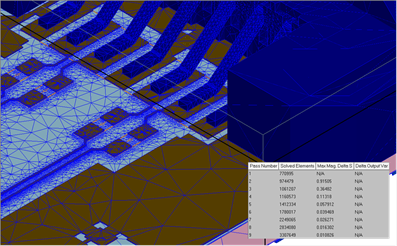

3D结合传统方式直接求解

该方法是把封装、PCB、連接器在3DL內全部以HFSS计算,有考虑这三部分彼此间的耦合。缺点除了求解时间长、耗用硬件资源多(RAM),还可能会因结构不同部分的尺寸比差异过大(超过1e+7),导致网格划分困难,甚至初始网格失败。

此例在[Design Settings] \ [HFSS Meshing Method] \ 设定[Phi Plus]可以轻易过关,但若以默认的[Phi mesh]或[Classic mesh]设定解算,则会计算(卡)很久。

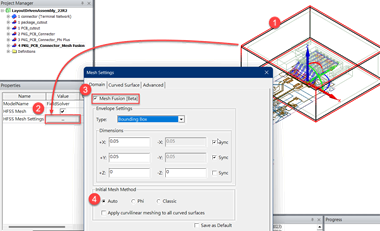

- 封装+PCB+连接器

3D结合以Mesh Fusion求解

这方法是把封装、PCB、连接器在3DL内全部以HFSS搭配[Mesh Fusion]求解,有考虑这三部分彼此间的耦合。 连接器以外用HFSS的[Phi mesh]解,而连接器本身以[Mesh Fusion]技术设置[Auto mesh]解。

在HFSS 3D环境内,对于HFSS 3D设计可以通过[Mesh Fusion]选[TAU]或[Classic] mesh,但在HFSS 3D Layout环境内,对于HFSS 3D设计透过[Mesh Fusion]只有[Phi]或[Classic]可选,没有[TAU]。

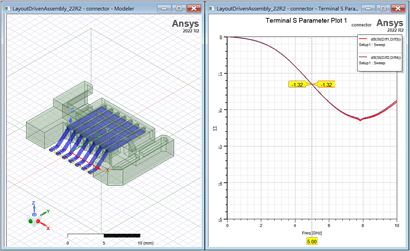

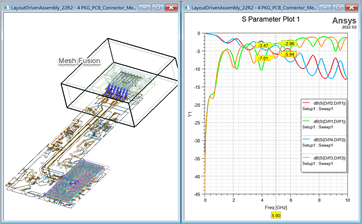

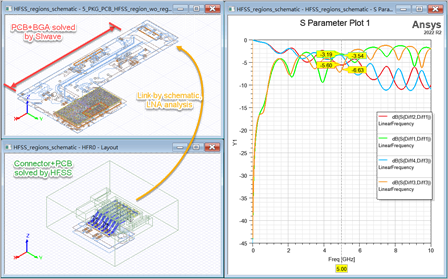

- 封装+PCB+连接器 以HFSS region+SIwave求解

这方法是连接器与连接器下方PCB以HFSS(HFSS region)计算,其余PCB与封装以SIwave解,有考虑连接器-PCB间与封装-PCB间的耦合。

诀窍是:一开始PCB与BGA封装贴合这步骤必须在SIwave内先做好后再输出到HFSS 3D Layout。 如果PCB与BGA封装贴合这步骤在HFSS 3D Layout内做(如本文方法二、三所示),会发生SIwave

solver无法识别DIE端环形的gap port。

- 结果对比

(一)方法一 vs. 方法二

l

方法一不考虑连接器-PCB、封装-PCB间的耦合,方法二有考虑三部份彼此间的上下耦合。

S参数:0Hz~5GHz差不多(在5GHz约差1~2dB),5G~10GHz则方法二偏较好(在10GHz约差6dB)。

求解时间:方法一以32G RAM/8核心笔记本电脑,全部解完只需要7~8分钟,而方法二以512G RAM/40核心工作站,全部解完的时间约十几小时,前者快了百倍速度。

(二)方法二 vs. 方法三

l

这两种方法都有考虑三部分彼此间的上下耦合。

S参数:0Hz~10GHz都相同。

求解时间:方法三最终收敛的网格数(last adaptive

mesh)330万,比起方法二最终收敛的网格数470万,少了30%,整个求解时间则节省约50%。

方法三[Mesh Fusion]是当需要全HFSS求解前提下的最佳选择。

尽可能使用较新版本的[Mesh Fusion],其解宽带SI题目的DC region准度会较好。

当有使用[Mesh Fusion]时,不只有refime mesh,连initial mesh都可分布式求解。

当有使用[Mesh Fusion]时,不只有refime mesh,连initial mesh都可分布式求解。

(三)方法三 vs. 方法四

这两种方法都有考虑上下耦合,但方法四由于是SIwave+HFSS协同求解,速度明显更快(约快40倍)。

S参数:0Hz~5GHz差不多(在5GHz约差0.2~0.4dB),5G~10GHz则方法四偏较好(在10GHz约差2dB)。

求解时间:方法四以64G RAM/8核心笔记本电脑,整个求解时间约十几分钟